1. DMA Memory Performance

The EDMA3 architecture is designed with multiple features to enable efficient parallel data transfers. This section explores the key factors that influence its performance, such as memory type, address offset, and other relevant parameters.

1.1 DMA Transfer Overhead

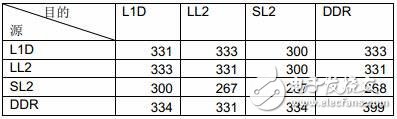

The general transmission delay refers to the time between when the EDMA is triggered and when the actual data transfer begins. Since measuring the exact start of a data transfer can be challenging, we use the completion time of the smallest data unit (one word) to estimate the overhead. This value varies depending on the source and destination addresses involved. Table 4 shows the average clock cycles measured from the EDMA Trigger (Write ESR) for a minimum data transfer (1 word) to the EDMA transfer end (read IPR=1), based on a 1GHz C6678 EVM (64-bit 1333MTS DDR).

Table 4: EDMA CC0 Transmission Overhead

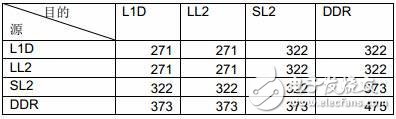

Table 5: EDMA CC1 and CC2 Transmission Overhead

EDMA CC0 is connected to an internal bus switching network closer to SL2 and DDR, resulting in lower overhead when accessing these memory types. In contrast, EDMA CC1 and CC2 are linked to a bus network closer to L1 and LL2 of the DSP core, which leads to lower overhead when accessing those memories. IDMA is typically used for copying data within LL2, and the average overhead for tested IDMA operations is around 61 clock cycles.

For small data transfers, the overhead of the DMA becomes a critical factor. The time taken to transfer a single data unit is almost entirely determined by this overhead. Therefore, for small data copies, it's important to weigh the trade-off between using the DMA and utilizing the DSP core directly.

1.2 Differences Between EDMA Transmission Engines

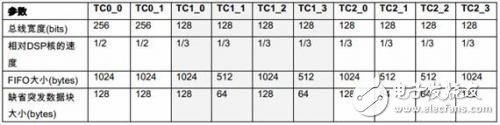

The C6678 chip includes 10 EDMA3 Transfer Controllers (TCs). These controllers are not all the same, and their performance characteristics differ. Table 6 summarizes the main differences among them.

Table 6: Differences Between EDMA Transmission Engines

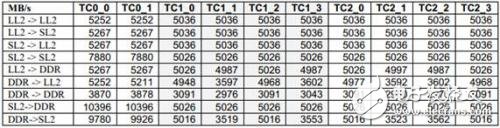

Table 7 compares the maximum throughput of each EDMA TC on a 1GHz C6678 EVM (64-bit 1333MTS DDR). The test parameters were ACNT=1024, BCNT=128, and AB_Sync (ACNT x BCNT transferred at once).

Table 7: EDMA TC Throughput Comparison on 1GHz C6678

When transferring data between SL2 and DDR, TC0_0 and TC0_1 achieve approximately twice the throughput of the other TCs. Unless otherwise specified, the EDMA performance data in this document is measured using TC0_0.

1.3 EDMA Bandwidth and Flexibility Trade-offs

EDMA3 supports various flexible configuration options for data transfers. While it can take full advantage of memory bandwidth in most configurations, some settings may lead to reduced performance. To design an efficient system, it’s essential to understand which configurations offer optimal performance and sometimes balance flexibility with efficiency.

1.3.1 Consideration of First Dimensional Size (ACNT) – Burst Block Size

To maximize the utilization of the transmission engine's bandwidth, it's crucial to transfer large blocks of data whenever possible.

To fully utilize the 128-bit or 256-bit bus, ACNT should be a multiple of 16 bytes. For optimal EDMA burst performance, ACNT should be a multiple of 64 bytes. To make the best use of the EDMA FIFO, ACNT should be at least 512 bytes.

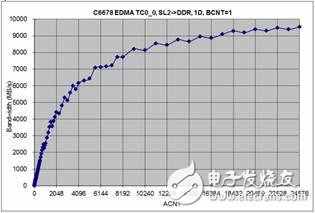

Figure 7 illustrates the measured throughput when transferring data ranging from 1 to 24K bytes from SL2 to DDR on a 1GHz C6678 EVM (64-bit 1333MTS DDR).

Figure 7: Effect of ACNT on EDMA Efficiency

As shown in the test results, larger ACNT values result in higher bandwidth utilization.

1.3.2 Two-Dimensional Transmission Considerations – Transmission Optimization

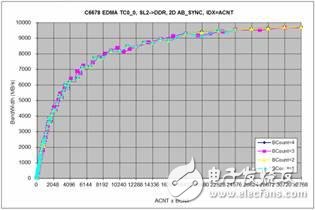

If a 2D transmission (AB_Sync) is linear (BIDX = ACNT) and ACNT is a power of two, EDMA will optimize the 2D transmission into a 1D one. We tested various combinations of ACNT and BCNT on a 1GHz C6678 EVM (64-bit 1333MTS DDR). Figure 8 shows the results of linear 2D transmission, demonstrating that the bandwidth is determined by the product of ACNT and BCNT, regardless of BCNT.

Figure 8: Linear 2D Transmission

If the 2D transmission is not linear, the bandwidth utilization is completely dependent on ACNT, as illustrated in Figure 7.

Applications

1. Residential: Used for off-grid power solutions, solar energy storage, and backup power.

2. Commercial: Essential for data centers, emergency lighting, and UPS systems.

3. Industrial: Supports processes requiring continuous power supply, such as manufacturing lines.

4. Grid-Scale: Critical for balancing the electrical grid, providing peak shaving, and facilitating renewable energy integration.

Advancements and Future Trends

Advancements in materials science and technology are driving improvements in battery efficiency, cost-effectiveness, and environmental impact. Research is focused on developing next-generation batteries that can offer higher energy densities, faster charging times, and longer lifespans, making them more viable for widespread adoption in various sectors.

Conclusion

Energy storage batteries are indispensable in today’s energy landscape, enabling the transition towards sustainable and resilient energy systems. As technology evolves, so do the capabilities of these batteries, promising a future where energy storage becomes even more efficient, reliable, and accessible.

Solar Battery Storage System,Battery Storage,Solar Battery Storage,Energy Storage System,Battery Energy Storage System,Cabinet Type Batteries

Ningbo Taiye Technology Co., Ltd. , https://www.tysolarpower.com