Micro-electromechanical (MEMS) gyroscopes are widely used in aviation, automotive automation, and consumer electronics. They are primarily categorized into linear vibrating gyros and rotating vibrating gyros based on their vibration structures. As the cost and power consumption of MEMS gyros continue to decrease, and their size and weight become smaller, new demands such as high precision and high sampling frequency have emerged for digitalization schemes. For MEMS gyros to operate at high frequencies, digital circuits must support high sampling rates. Currently, the digitization of MEMS gyros is mainly achieved through embedded Field Programmable Gate Arrays (FPGAs), Digital Signal Processors (DSPs), or a combination of both.

In testing scenarios, MEMS gyroscopes are verified on platforms that allow signal demodulation and control to be performed on the PC side. This approach offers greater convenience compared to traditional FPGA or DSP-based systems. High-speed data transmission between the PC and capture card is facilitated via the PCIe (PCI Express) bus, achieving a maximum control delay of less than 10μs.

### Computer-Based Low-Speed Optimization for Real-Time Control Systems

Real-time performance is a critical factor in gyro measurement and control systems. This section focuses on designing and optimizing low-latency and stable control systems. The first part of the optimization involves hardware and software improvements. Hardware optimization includes selecting the right high-speed bus type and efficient transmission control methods. Software optimization covers operating system driver-level enhancements and refinement of control algorithms.

The second part of the optimization focuses on ensuring the stability of the computer-based real-time control system, allowing it to consistently generate output signals. In practical engineering, the system must prevent disruptions caused by interrupt delays and fluctuating transmission times.

### 1.1 Low-Latency Optimization in Data Transmission

**Figure 1: Low-latency optimization scheme for real-time measurement and control platform**

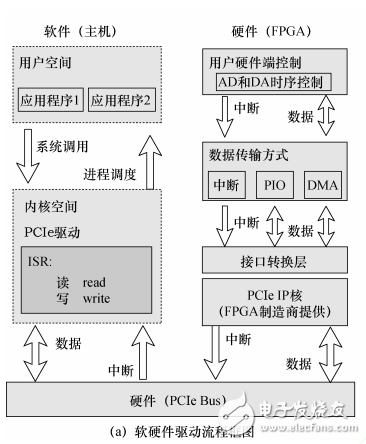

Figure 1a illustrates the hardware and software framework along with the data flow of the real-time measurement and control platform. Once a hardware interrupt is triggered, the data collected by the ADC must pass through the interface conversion layer, the FPGA's PCIe IP core, and the PCIe bus before reaching the computer’s IO memory space. After memory address mapping is completed, the user program can read the data from memory for further processing.

In actual multi-threaded data transfers, additional delays occur, as shown in Figure 1b. These include interrupt latency, thread latency, and thread context switch latency. Interrupt latency refers to the time difference between when the hardware interrupt is executed and when the first instruction of the Interrupt Service Routine (ISR) starts. It is influenced by factors such as kernel architecture, CPU frequency, and load. Due to thread scheduling, the kernel requires preparation time for saving and restoring thread contexts, acquiring or releasing semaphores, and similar tasks.

Thread latency is defined as the time difference between when a thread is signaled to wake up in the ISR and when it begins executing its first instruction. Thread context switch latency refers to the time between the execution of the first instruction of one thread and the first instruction of the next thread. Understanding and minimizing these latencies is essential for achieving a robust and responsive real-time control system.

Spot Lights Moving Head ,Led Moving Head Spot,Moving Head Spotlight,Spot Moving Head Light

Guangzhou Cheng Wen Photoelectric Technology Co., Ltd. , https://www.cwledwall.com