Signal integrity is a critical system engineering discipline that focuses on analyzing and mitigating the adverse effects of noise, distortion, and signal loss in high-speed digital communication links. It plays a vital role in ensuring the performance and reliability of high-speed systems. However, maintaining electrical performance integrity remains a major challenge in the "Siege Lion" of high-speed circuit design. Experienced engineers, often referred to as "old birds," are able to apply signal integrity principles effectively and use simulation and testing tools to quickly resolve various circuit issues.

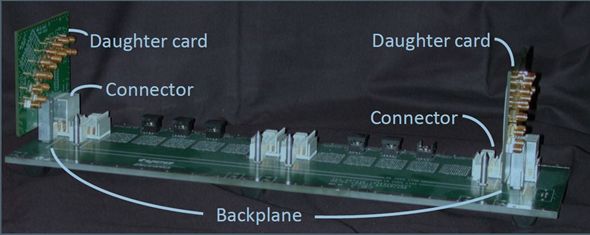

Today, we’re going to walk you through the essential tools and provide hands-on video tutorials to help your technology level take a big leap forward. In high-speed digital signal transmission, a channel refers to the entire electronic path from the transmitter's IO buffer to the receiver’s IO buffer. This can include chip packages, PCB traces, connectors, and cables. A simple channel might consist of a direct path from the transmitter to the receiver, while a more complex channel, like a backplane, may involve multiple components, as shown in Figure 1.

When modeling a channel, it's important to focus on three key characteristics: impedance, loss, and delay or phase. Impedance is determined by the mechanical structure, dielectric constant, and conductivity of the materials used. Mismatches in impedance can lead to reflections, causing signal ringing, overshoot, and undershoot. Additionally, channel loss is crucial for SERDES design. The primary sources of signal loss are dielectric and conductor losses, which are typically frequency-dependent. As a result, the bandwidth of a channel limits the maximum bit rate it can support. For DDR systems, controlling the phase difference between command, address, clock, DQ, and DQS signals is essential.

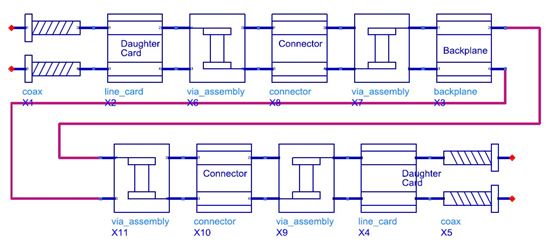

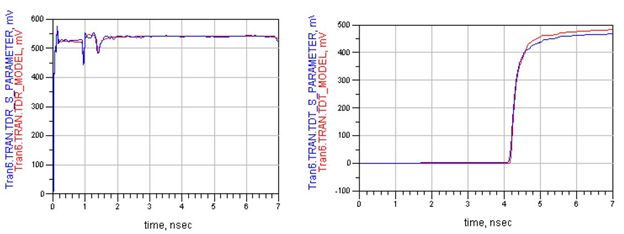

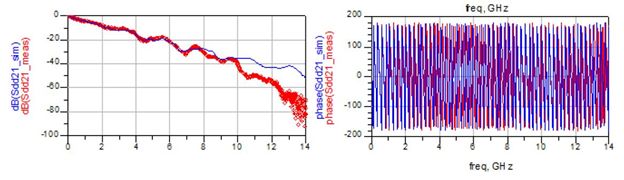

The components of a channel can be modeled using formula-based transmission line models, electromagnetic simulations, or measurement-based models. The accuracy of each model depends on the precision of material parameters and component sizes. Once individual components are accurately modeled, they can be cascaded to form a complete channel model, as shown in Figure 2. Impedance and delay can be estimated through TDR simulations (as seen in Figure 3), while insertion loss can be analyzed via S-parameter simulations (as shown in Figure 4). These results offer valuable insights for optimizing the channel and enabling higher data rates.

By now, you should have a clearer understanding of how to model a high-speed channel. But how exactly do you do it? The video below will guide you step-by-step on building a high-speed channel model with specific frequency loss.

(Want to learn more about ADS for signal integrity and power integrity analysis? More details will follow.)

After reading this, do you feel more confident in using ADS to build a high-speed channel model? With such a model, you can freely adjust link parameters and observe their impact on the model’s behavior, ultimately identifying the optimal solution. Once the simulation and optimization are complete, the results must be applied to the actual circuit, with necessary debugging based on real-world conditions to ensure the final product meets expectations.

At this stage, Keysight’s oscilloscope becomes an essential tool for testing and characterizing various signal metrics, helping speed up the verification process. Moreover, experienced engineers often look beyond just the current design—they aim to predict the outcome before the new board is manufactured, improving efficiency, reducing costs, and shortening the product launch cycle.

Keysight’s oscilloscope offers another powerful tool—N8900A offline software. After using ADS for link simulation and obtaining S-parameters, the model can be imported into N8900A. This allows the measured signal eye diagram of the high-speed link front end to be embedded and de-embedded, facilitating the evaluation of the Siege Lion’s high-speed link model and its real-world impact. This helps identify key debugging directions and improve overall performance.

182mm Mono Solar Panel

From the upgrade of the existing 158.75 and 166 production lines, the process span of 182 solar panels is smaller, and the existing equipment and processes are more mature. Therefore, the difficulty and cost of new or upgraded production lines are lower, and the product yield rate is currently normal. PV industry experts suggest that the advantage of 182mm is that the industrial ecology is more mature, and it is the optimal size silicon wafer that meets the current development level of upstream and downstream, and is the first choice at this stage.

Sunket 182mm Solar Panel use 182mm 10BB/11BB Solar Cell, increases the wafer size, optimizes the layout profoundly and decreases the invalid power generation area.

1.Half Cell Technology

The half-cut cell design can decrease the power loss by the shadow effectively. The optimized circuit design not only realizes the maximum power output but also assures the reliability of solar panels.

2.MBB Technology

Sunket 182mm Solar Panel adopts multi-busbar technology. More busbars of the cell decrease the current transverse propagation path by 50%, effectively reduce the internal loss, and improve power of solar panels.

182mm Solar Panel,Mono Solar Panel,182mm Mono Solar Panel,Solar PV Module,Solar Panel

Wuxi Sunket New Energy Technology Co.,Ltd , https://www.sunketsolar.com